Microprocessors

Basic Microprocessor Terminology

Learning Objectives:

- Familiarize yourself with the key components of a microprocessor, including the arithmetic logic unit (ALU), control unit, registers, and buses.

- Learn about different types of registers, including the program counter (PC), stack pointer (SP), and general-purpose registers, and their roles in microprocessor operation.

- Comprehend the functions of the address bus and data bus in microprocessor communication with memory and peripherals.

Bit: A bit is a single binary digit.

Word: A word refers to the basic data size or bit size that can be processed by the arithmetic and logic unit of the processor. A 16-bit binary number is called a word in a 16-bit processor.

Bus: A bus is a group of wires/lines that carry similar information.

System Bus: The system bus is a group of wires/lines used for communication between the microprocessor and peripherals.

Memory Word: The number of bits that can be stored in a register or memory element is called a memory word.

Address Bus: It carries the address, which is a unique binary pattern used to identify a memory location or an I/O port. For example, an eight bit address bus has eight lines and thus it can address 2\(^8\) = 256 different locations. The locations in hexadecimal format can be written as 00H – FFH.

Data Bus: The data bus is used to transfer data between memory and processor or between I/O device and processor. For example, an 8-bit processor will generally have an 8-bit data bus and a 16-bit processor will have 16-bit data bus.

Control Bus: The control bus carry control signals, which consists of signals for selection of memory or I/O device from the given address, direction of data transfer and synchronization of data transfer in case of slow devices.

Solved Example: 8953-01

What is the purpose of the clock signal in a microprocessor?

A. Power the CPU

B. Set operation timings

C. Increase voltage

D. Reduce heat

Correct Answer: B

Solved Example: 8953-02

An accumulator is used to:

A. Store output devices

B. Store temporary data during ALU operations

C. Accumulate addresses

D. Increase clock speed

Correct Answer: B

Solved Example: 8953-03

The width of the data bus determines:

A. The number of instructions

B. The amount of memory addressable

C. The amount of data transferred at a time

D. The number of peripherals connected

Correct Answer: C

Solved Example: 8953-04

A "fetch" operation in the CPU refers to:

A. Sending data to output

B. Retrieving an instruction from memory

C. Performing a calculation

D. Storing data in cache

Correct Answer: B

Solved Example: 8953-05

Which unit interprets and sends control signals to other parts of the processor?

A. ALU

B. Register Bank

C. Control Unit

D. Clock

Correct Answer: C

Solved Example: 8953-06

In microprocessor terminology, "opcode" refers to:

A. Operand value

B. Memory address

C. Operation code

D. Output signal

Correct Answer: C

Solved Example: 8953-07

What is the function of the Stack Pointer (SP)?

A. Point to the program counter

B. Keep track of function calls

C. Point to the top of the stack

D. Track instruction memory

Correct Answer: C

Solved Example: 8953-08

The Instruction Register (IR) stores:

A. The result of an operation

B. Memory address

C. The currently executing instruction

D. The clock frequency

Correct Answer: C

Solved Example: 8953-09

A collection of wires used to transmit signals is known as a:

A. Port

B. Bus

C. Register

D. Loop

Correct Answer: B

Solved Example: 8953-10

The temporary storage area in a microprocessor is called a:

A. Cache

B. Register

C. Stack

D. Buffer

Correct Answer: B

Solved Example: 8953-11

Which bus is responsible for carrying memory addresses?

A. Data Bus

B. Address Bus

C. Control Bus

D. Instruction Bus

Correct Answer: B

Solved Example: 8953-12

The binary instruction that a microprocessor executes is known as:

A. Bytecode

B. Source code

C. Machine code

D. Microcode

Correct Answer: C

Solved Example: 8953-13

What is the function of the Control Unit (CU)?

A. Store data temporarily

B. Perform arithmetic operations

C. Coordinate execution of instructions

D. Store program code

Correct Answer: C

Solved Example: 8953-14

Which register keeps track of the next instruction to execute?

A. Instruction Register

B. Program Counter

C. Stack Pointer

D. Accumulator

Correct Answer: B

Solved Example: 8953-15

What does ALU stand for in a microprocessor?

A. Arithmetic Logic Unit

B. Analog Load Unit

C. Address Link Unit

D. Auxiliary Line Unit

Correct Answer: A

Solved Example: 9173-01

8085 is a/an ______ -bit processor.

A. 8

B. 16

C. 24

D. 64

8085 is an 8 bit microprocessor whereas 8086 is a 16 bit microprocessor.

Correct Answer: A

Solved Example: 9173-02

Which of the following is a 16-bit register in 8085 processor?

- Stack pointer

- Program counter

- Accumulator

A. 1. only

B. 2. only

C. 2. and 3.

D. 1. and 2.

In 8085, the accumulator is 8 bit, whereas Program counter and stack pointer, since they represent address locations, they are 16 bit.

Correct Answer: D

8085 Microprocessor Architecture

Learning Objectives:

- Understand the main components and working principles of the Intel 8085 microprocessor,

- Understand the basic computer architecture.

Appaloosa, CC BY-SA 3.0, via Wikimedia Commons

The 8085 microprocessor is an 8-bit processor available as a 40-pin IC package and uses +5 V for power. It can run at a maximum frequency of 3 MHz. Its data bus width is 8-bit and address bus width is 16-bit, thus it can address 2\(^{16}\) = 64 KB of memory.

Arithmetic and Logic Unit: The ALU performs the actual numerical and logical operations such as Addition (ADD), Subtraction (SUB), AND, OR etc. It uses data from memory and from Accumulator to perform operations. The results of the arithmetic and logical operations are stored in the accumulator.

Registers: The 8085 includes six registers, one accumulator and one flag register. In addition, it has two 16-bit registers: stack pointer and program counter. They are briefly described as follows. The 8085 has six general-purpose registers to store 8-bit data; these are identified as B, C, D, E, H and L. they can be combined as register pairs - BC, DE and HL to perform some 16 bit operations. The programmer can use these registers to store or copy data into the register by using data copy instructions.

Accumulator: The accumulator is an 8-bit register that is a part of ALU. This register is used to store 8-bit data and to perform arithmetic and logical operations. The result of an operation is stored in the accumulator. The accumulator is also identified as register A.

Flag register: The ALU includes five flip-flops, which are set or reset after an operation according to data condition of the result in the accumulator and other registers. They are called Zero (Z), Carry (CY), Sign (S), Parity (P) and Auxiliary Carry (AC) flags. The microprocessor uses these flags to test data conditions.

Program Counter (PC): This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer. The microprocessor uses this register to sequence the execution of the instructions. The function of the program counter is to point to the memory address from which the next byte is to be fetched. When a byte is being fetched, the program counter is automatically incremented by one to point to the next memory location.

Stack Pointer (SP): The stack pointer is also a 16-bit register, used as a memory pointer. It points to a memory location in R/W memory, called stack. The beginning of the stack is defined by loading 16- bit address in the stack pointer.

Instruction Register/Decoder: It is an 8-bit register that temporarily stores the current instruction of a program. Latest instruction sent here from memory prior to execution. Decoder then takes instruction and decodes or interprets the instruction. Decoded instruction then passed to next stage.

Control Unit: Generates signals on data bus, address bus and control bus within microprocessor to carry out the instruction, which has been decoded.

Stefan506 (dewiki userpage), CC BY-SA 3.0, via Wikimedia Commons

Solved Example: 9955-01

8085 is a/an ______ -bit processor.

A. 8

B. 16

C. 24

D. 64

Correct Answer: A

Solved Example: 9955-02

Which of the following is a 16-bit register in 8085 processor?

- Stack pointer

- Program counter

- Accumulator

A. 1 only

B. 2 only

C. 2 and 3

D. 1 and 2

Correct Answer: D

Solved Example: 9955-03

The clock frequency of an 8085 microprocessor is 5 MHz. If the time required to execute an instruction is 1.4 $\mu$s, then the number of T-states needed for executing the instruction is:

A. 1

B. 6

C. 7

D. 4

Correct Answer: C

Solved Example: 9955-04

The 8085 Microprocessor has:

A. 8 - bit data bus 16 - bit address bus

B. 8 - bit data bus 8 - bit address bus

C. 16 - bit data bus 8 - bit address bus

D. 16 - bit data bus 16 - bit address bus

Correct Answer: A

Solved Example: 9955-05

Accumulator in 8085 is __ bit register.

A. 16

B. 12

C. 8

D. 4

Correct Answer: C

Solved Example: 9955-06

In 8085 microprocessor, _____ interrupt has the lowest priority?

A. INTR

B. TRAP

C. RST 7.5

D. RST 5.5

Correct Answer: A

Solved Example: 9955-07

Which of the following is an advantage of multiple bus organisations over single bus?

A. Instruction fetch is faster

B. Reduction in the number of cycles for execution.

C. Instruction decoding is faster

D. Data path becomes complex

In multiple bus structure, two buses are used, one for communication from peripherals and the other for the processor. The number of cycles for execution is less compared to single bus structure.

Correct Answer: B

Instruction Set in 8085

Learning Objectives:

- To become familiar with the instruction set of Intel 8085 Microprocessor.

Data transfer operations: This group of instructions copies data from source to destination. The content of the source is not altered.

Examples are: MOV, MVI, LXI, LDA, STA, etc.Arithmetic operations: Instructions of this group perform operations like addition, subtraction, increment and decrement. One of the data used in arithmetic operation is stored in accumulator and the result is also stored in accumulator.

Examples: ADD, SB, INR, DADLogical operations: Logical operations include AND, OR, EXOR, NOT. The operations like AND, OR and EXOR uses two operands, one is stored in accumulator and other can be any register or memory location. The result is stored in accumulator. NOT operation requires single operand, which is stored in accumulator.

Examples are: ANA, XRA, ORA, CMP, RALBranching operations: Instructions in this group can be used to transfer program sequence from one memory location to another either conditionally or unconditionally.

Examples are: JMP, JC, CALL, CZ, RST, etc.Machine control operations: Instruction in this group control execution of other instructions and control operations like interrupt, halt etc.

Examples are: IN, OUT, PUSH, POP, HLT, etc.

Solved Example: 9985-01

Which of the following instructions is NOT used for data copy/transfer in microprocessor?

A. MOV

B. POP

C. DAS

D. PUSH

DAS (Decimal Adjust after Subtraction) is an arithmetic instruction.

Correct Answer: C

Solved Example: 9985-02

PUSH and POP operations are performed by:

A. Program counter register

B. General purpose register

C. Stack pointer register

D. Link register

With a stack, all operations are done at the "top" of the stack. The "push" operation adds an element to the top of the stack. The "pop" operation removes and returns an element from the top of the stack. The register associated with the stack is the stack pointer.

Correct Answer: C

Solved Example: 9985-03

The contents to the register pair DE after the execution of the following Intel 8085 instructions, is

PUSH H; PUSH D; POP H; POP DA. [H] → [D] ; [L] → [E]

B. [A] → [D] ; [B] → [E]

C. [H] → [D] ; [A] → [E]

D. [L] → [D] ; [H] → [E]

PUSH Operation:

Decrement SP and PUSH RP$_H$.

Decrement SP and PUSH RP$_L$.

POP Operation:

Get 1 byte from stack to RP$_L$ and increment.

Get 1 byte from stack to RP$_H$ and increment.

Correct Answer: A

Solved Example: 9985-04

What is the content of accumulator of 8085 microprocessor after the execution of $XRI F0_H$ instruction?

A. Only the upper nibble of accumulator is complemented

B. Only the lower nibble is complemented

C. Only the upper nibble is reset to zero

D. Only the lower nibble is reset to zero

Correct Answer: A

Solved Example: 9985-05

How many T states are required to execute STA 1234 instruction:

A. 7 T

B. 4 T

C. 10 T

D. 13 T

Correct Answer: D

Solved Example: 9985-06

The number of machine cycles required for the execution of STA instruction are:

A. 6

B. 4

C. 13

D. 3

Correct Answer: B

Solved Example: 9985-07

A fetch cycle is the:

A. First part of the instruction cycle

B. Last part of the instruction cycle

C. Intermediate part of the instruction cycle

D. Auxiliary part of the instruction cycle

Correct Answer: A

Solved Example: 9985-08

The number of cycles required to execute the given instruction is: \[MOV DPTR,#data16\]

A. 3

B. 2

C. 4

D. 1

Correct Answer: B

Solved Example: 9985-09

While execution of IN/OUT instruction takes place, the 8-bit address of the port is placed on:

A. Lower address bus

B. Higher address bus

C. Data bus

D. Lower as well as higher order address bus

Correct Answer: D

Solved Example: 9985-10

In an 8085 microprocessor, the contents of the accumulator and the carry flag are A7 (in hex) and 0, respectively. If the instruction RLC is executed, then the contents of the accumulator (in hex) and the carry flag, respectively, will be:

A. 4E and 0

B. 4E and 1

C. 4F and 0

D. 4F and 1

Correct Answer: D

Solved Example: 9985-11

If a program with 5 instructions is executed in 7 clock cycles, then CPI is:

A. 1.4

B. 1.5

C. 1

D. 2

Correct Answer: A

Solved Example: 9985-12

The difference between 8085 instructions RST n and PCHL is:

A. RST n is equivalent to a sub-routine call while PCHL is equivalent to unconditional branch

B. RST n uses direct addressing while PCHL uses register indirect addressing

C. RST n is a software interrupt while PCHL simulates a hardware interrupt

D. RST n resets the processor while PCHL restarts the processor

Correct Answer: A

Solved Example: 9985-13

The 8085 assembly language instruction that stores the contents of H and L registers into the memory locations 2050H and 2051H, respectively, is:

A. SPHL 2050 H

B. SPHL 2051 H

C. SHLD 2050 H

D. STAX 2050 H

Correct Answer: C

Solved Example: 9985-14

What is the meaning of Instruction DAD B?

A. Register A is added with Register B

B. Register pair BC is added with register pair BC

C. Decimal Adjustment of Register B

D. Register pair HL is added with register Pair BC

This command adds the contents of the HL register pair to the specified register pair (Rp) and stores the resulting result in the HL register pair.

Correct Answer: D

Solved Example: 9985-15

Following instruction is executed in 8085: \[\mathrm{LDB}\ 4000_H\]

Identify the correct statement.

A. 4000$_H$ is copied to register B

B. Data at address 4002$_H$ is copied to register B

C. 4002$_H$ is copied to register B

D. Data at address 4000$_H$ is copied to register B

LDB = Load the register B with the contents from the memory. That means, data at address 4000$_H$ is copied to register B.

Correct Answer: D

Solved Example: 9985-16

The 8085 instruction that doubles the value in accumulator is:

A. XRA A

B. ADD A

C. SUB A

D. ORA A

Let us see each option individually.

- XRA A: Performs bit wise XOR operation between source operand and destination operand and store the result in the accumulator. Here, source and destination operand both are same i.e. A. Therefore, the result after performing XOR operation, the value stored in the accumulator is 00.

- ADD A: Adds the contents of source operand to the contents of accumulator and store the result in the accumulator itself. Since, the source and destination operand are same, the value of accumulator will get double.

- SUB A: Subtracts the contents of source operand from the contents of accumulator and store the result in the accumulator itself. Since, the source and destination operand are same the value of accumulator A = 00.

- ORA A: Performs bit wise OR operation between source operand and destination operand and store the result in the accumulator. Here, source and destination operand both are same i.e. A. Therefore, the result after performing OR operation, stored in the accumulator remains same.

Correct Answer: B

Solved Example: 9985-17

For 8085 microprocessor, if register B has 65 H and accumulator has 97 H, what will be content of a accumulator after executing instruction SUB B?

A. 65$_H$

B. 97$_H$

C. 32$_H$

D. 28$_H$

SUB = Subtract contents of R from Accumulator.

SUB B = A - B = (97$_H$ - 65$_H$) = 32$_H$

Correct Answer: C

Solved Example: 9985-18

The RST 3 instruction in Microprocessor IC 8085 is equivalent to:

A. CALL 0028$_H$

B. CALL 0030$_H$

C. CALL 0020$_H$

D. CALL 0018$_H$

RST n = Restart n where n = {1,2, ...,7}

RST n = CALL n $\times 8$

Here, RST 3 = RST 3 $\times$ 8 = RST CALL 0018$_H$

Correct Answer: D

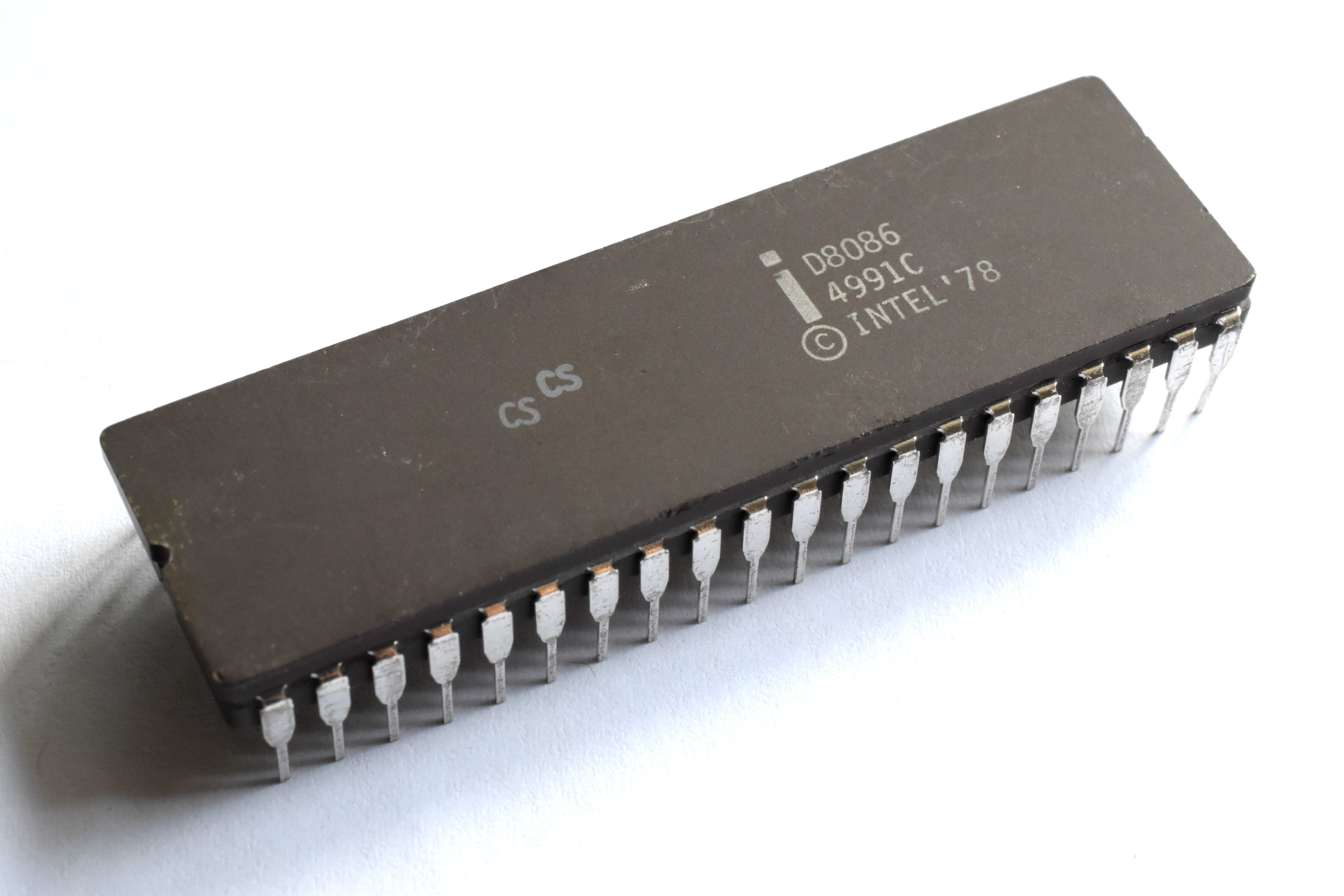

8086 Microprocessor Architecture and Operation

Learning Objectives:

- Explore the instruction set architecture of the 8086 microprocessor, including the various instructions and their formats.

- Learn how the 8086 microprocessor communicates with input and output devices, including the role of I/O ports and instructions.

- Learn how the 8086 microprocessor executes instructions, including the fetch-decode-execute cycle.

- It is a 16 bit microprocessor.

- 8086 has a 20 bit address bus can access upto 220 memory locations (1 MB).

- It can support upto 64K I/O ports.

- It provides 14, 16-bit registers. It has multiplexed address and data bus AD0- AD15 and A16 – A19.

- It requires single phase clock with 33% duty cycle to provide internal timing.

- 8086 is designed to operate in two modes, Minimum and Maximum.

- It can prefetch upto 6 instruction bytes from memory and queues them in order to speed up instruction execution.

- It requires +5V power supply. A 40 pin dual in line package.

Thomas Nguyen, CC BY-SA 4.0, via Wikimedia Commons

Solved Example: 9984-01

Direction flag is used with:

A. String instructions

B. Stack instructions

C. Arithmetic instructions

D. Branch instructions

- If DF is set 1, then it accesses the string data from higher memory location towards lower memory location.

- If DF is reset to 0, then it accesses the string data from the lower memory location towards the higher memory location.

Correct Answer: A

Solved Example: 9984-02

In 8086 microprocessor, if DS = 1100H, BX = 0200 H and SI = 0500H, the address accessed by MOV CH, [BX + SI] is:

A. 00300 H

B. 11700 H

C. 0700 H

D. 01800 H

Correct Answer: B

Solved Example: 9984-03

The stack pointer will be affected by instructions:

1. PUSH PSW

2. CALL ADDR

3. XTHL

4. RST n

A. 1, 2, 3 and 4

B. 1 and 3 only

C. 1, 2 and 4 only

D. 2, 3 and 4 only

Correct Answer: C

Solved Example: 9984-04

Assertion (A): Architecturally 8086 μP is totally different from its predecessor 8085 μP but functionally it is downward compatible with 8085.

Reason (R): The segmented architecture was introduced in 8086 μP to keep compatibility with 8085 μp.

A. Both (A) and (R) are true and (R) is the correct explanation of (A)

B. Both (A) and (R) are true, but (R) is not the correct explanation of (A)

C. (A) is true, but (R) is false

D. (A) is false, but (R) is true

Correct Answer: A